在过去二十年中,碳化硅(SiC)材料和功率器件的发展导致SiC器件在电力电子中的使用更加高效和具有成本效益。进展可以用性能、可靠性、成本和铸造模型来表示。在本文中,我们总结了我们小组之前发表的关于SiC MOSFET可靠性的工作,并酌情添加了一些新数据。

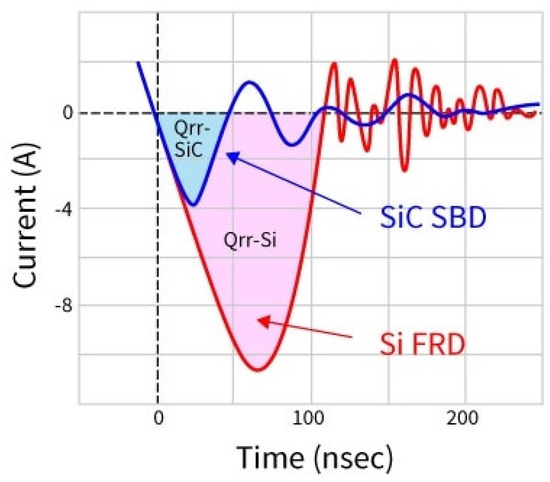

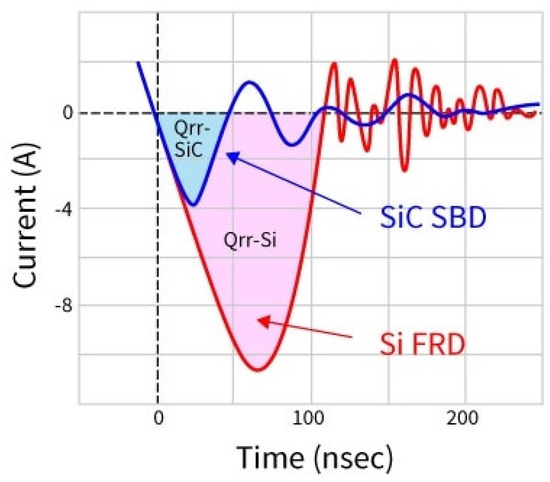

众所周知,硅功率器件在过去几十年中主导了半导体行业[4]。在快速开关和低损耗是重要指标的电力电子应用中,硅器件正逐渐被SiC和GaN器件取代。目标是用SiC和GaN单极器件(仅电子传导电流)取代硅双极器件(电子和空穴传导电流)。由于反向恢复电荷高,硅PIN二极管和IGBT如图1所示;会产生开关损耗,进而降低电力电子转换器的效率。相比之下,肖特基势垒二极管(SBD)和MOSFET等SiC器件具有最小的反向恢复电荷(QRR)和尾部电流,这分别导致给定开关频率下的开关损耗降低。此外,SiC MOSFET没有0.7 V硅IGBT结降,因此导通损耗较低。因此,使用SiC器件的每次功率转换效率(考虑3 V器件)可提高约1200%,并且这一优势随着电压的增加而增长。这一优势在电池电动汽车(BEV)中增长到约7%的往返效率[9],这就是SiC功率MOSFET和SBD在BEV中大规模适应的原因。

上述讨论指出,硅PIN二极管和IGBT(600 V至6.5 kV)可以用SiC SBD和MOSFET(600 V至12 kV范围)代替。例如,在开关模式电源等应用中,SiC SBD现在被用来代替硅PIN二极管,在这些应用中,开关损耗是一个关键问题。我们没有提到使用SiC PIN二极管和IGBT,因为这些SiC器件由于存在基底平面位错(BPD)仍然不可靠。BPD引起的堆叠故障会缩短寿命,增加导通电阻,并导致SiC PIN二极管和IGBT中的漏电流增加。

应该注意的是,低开关损耗允许更高的开关频率以及更小的转换器尺寸,作为效率增益的权衡。在BEV、光伏(PV)转换器和电源等一些应用中,更高的效率更有用。另一方面,在飞机、航天器、无人机、高速电机变速电机驱动器和电源适配器等应用中,通过提高开关频率以牺牲效率增益为代价来实现更小的尺寸。

碳化硅MOSFET栅氧化层外在缺陷的筛选

SiC外延层的表面可能包含许多表面缺陷,例如颗粒夹杂物,凹坑,Si脱落等,当SiC表面被氧化时,这些缺陷又转化为栅氧化层中的缺陷,并可能导致栅氧化层过早分解。这些缺陷称为外在缺陷。完成器件处理后,筛选出具有外部缺陷的器件至关重要,所有供应商都通过栅极电压筛选来实现这一点。栅极屏蔽方法是通过在极短时间内(<1 s)施加高压来去除晶圆级具有外在氧化物缺陷的器件的方法之一。具有外部缺陷的设备将导致短路或开路,并且可以将其从进一步考虑中移除。施加的栅极电压越高,可以消除的具有外在缺陷的器件就越多。因此,现场的故障率,称为FIT率(每十亿个设备运行小时的故障),可以降低,如图所示。对于平面MOSFET,栅极氧化层厚度约为40 nm,因此只能在栅极上施加约34 V(最大栅氧化场为8.5 MV/cm,以避免栅氧化层中的冲击电离或栅极注入空穴。8.5 MV/cm的值,已被用于保护制造过程中栅极氧化物变化的带)。因此,平面MOSFET的屏蔽电压与使用电压之比约为1.5。因此,栅极电压屏蔽可能无法有效消除许多外在缺陷,从而导致现场FIT率更高。另一方面,英飞凌的沟槽MOSFET具有更厚的栅氧化层(通常为70 nm),因为逆温层沿垂直平面的迁移率更高。因此,屏蔽电压可以高达60 V,以维持8.5 MV/cm的氧化物电场。因此,沟槽MOSFET的屏蔽电压与使用电压之比约为8,与平面设备相比,沟槽设备的FIT速率降低可以小三个数量级。这意味着大多数外部缺陷可以通过施加更高的屏蔽栅极电压来消除,从而使通过屏蔽的器件高度可靠。此外,如果我们将平面MOSFET的器件结构(这是许多供应商的标准)与英飞凌的沟槽式MOSFET进行比较,如图所示,可以清楚地注意到,平面MOSFET的间距要高得多,并且与沟槽MOSFET相比,栅极氧化物暴露在表面上更高密度的外在缺陷中。这意味着,对于相同的额定电流,沟槽MOSFET的尺寸将小约18×,并且暴露于外源缺陷的可能性要小得多;显示了由外延供应商提供的典型缺陷图,表示晶圆表面的高缺陷密度和低缺陷密度。大设备区域和小设备区域已叠加在缺陷图上。显然,具有大型器件和高缺陷密度的晶圆会导致良率大大降低。显然需要专注于减少外延层中的表面缺陷,以允许电动汽车和其他需要高电流的应用所需的更高电流MOSFET。英飞凌的沟槽MOSFET不易出现表面缺陷,这为大面积器件制造提供了非常明显的优势。

1.SiC器件的结构和特征!

Si材料中,越是高耐压器件其单位面积的导通电阻就越大(通常以耐压值的大概2-2.5次方的比例增加),因此600V以上的电压中主要采用IGBT(绝缘栅极双极型晶体管)。IGBT通过电导率调制,向漂移层内注入作为少数载流子的空穴,因此导通电阻比MOSFET还要小,但是同时由于少数载流子的积聚,在关断时会产生尾电流,从而造成极大的开关损耗。

SiC器件漂移层的阻抗比Si器件低,不需要进行电导率调制就能够以高频器件结构的MOSFET实现高耐压和低阻抗。而且MOSFET原理上不产生尾电流,所以用SiC MOSFET替代IGBT时,能够明显地减少开关损耗,并且实现散热部件的小型化。另外,SiC MOSFET能够在IGBT不能工作的高频条件下驱动,从而也可以实现被动器件的小型化。与600V~1200V的Si MOSFET相比,SiC MOSFET的优势在于芯片面积小(可以实现小型封装),而且体二极管的恢复损耗非常小。

2.SiC Mosfet的导通电阻

SiC的绝缘击穿场强是Si的10倍,所以能够以低阻抗、薄厚度的漂移层实现高耐压。因此,在相同的耐压值的情况下,SiC可以得到标准化导通电阻(单位面积导通电阻)更低的器件。例如900V时,SiC‐MOSFET的芯片尺寸只需要Si‐MOSFET的35分之1、SJ‐MOSFET的10分之1,就可以实现相同的导通电阻。不仅能够以小封装实现低导通电阻,而且能够使门极电荷量Qg、结电容也变小。目前SiC器件能够以很低的导通电阻轻松实现1700V以上的耐压。因此,没有必要再采用IGBT这种双极型器件结构(导通电阻变低,则开关速度变慢),就可以实现低导通电阻、高耐压、快速开关等各优点兼备的器件。

碳化硅mos的技术难点

综合各种报道,难题不在芯片的原理设计,特别是芯片结构设计解决好并不难。难在实现芯片结构的制作工艺。当然对于用户最直接的原因是,

SiC MOSFET的价格相对较高。